## **Cambridge Assessment International Education**

Cambridge International Advanced Subsidiary and Advanced Level

COMPUTER SCIENCE 9608/32

Paper 3 Written Paper

October/November 2017

MARK SCHEME

Maximum Mark: 75

## **Published**

This mark scheme is published as an aid to teachers and candidates, to indicate the requirements of the examination. It shows the basis on which Examiners were instructed to award marks. It does not indicate the details of the discussions that took place at an Examiners' meeting before marking began, which would have considered the acceptability of alternative answers.

Mark schemes should be read in conjunction with the question paper and the Principal Examiner Report for Teachers.

Cambridge International will not enter into discussions about these mark schemes.

Cambridge International is publishing the mark schemes for the October/November 2017 series for most Cambridge IGCSE<sup>®</sup>, Cambridge International A and AS Level components and some Cambridge O Level components.

${\rm I\!R}$  IGCSE is a registered trademark.

図 Cambridge Assessment す International Education

[Turn over

© UCLES 2017

| Question | Answer                                                                                                                                                                                                                                                                                                                                                                                                                              |      |           |     | Marks |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-----|-------|--|--|--|

| 1(a)     | Router  T Computer B Computer C Computer C Computer C Computer C C C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                |      |           |     |       |  |  |  |

| 1(b)     | The terminators do not need to be labelled as long as the                                                                                                                                                                                                                                                                                                                                                                           |      | T         | 1   | 4     |  |  |  |

| 1(6)     | Statement  The server can send packets to Computer B and the router at the same time.                                                                                                                                                                                                                                                                                                                                               | True | False   ✓ | (1) | 7     |  |  |  |

|          | Computer C uses the IP address of a web server to send a request for a web page on the web server                                                                                                                                                                                                                                                                                                                                   | ✓    |           | (1) |       |  |  |  |

|          | Computer B can read a packet sent from Computer A to Computer C. (1)                                                                                                                                                                                                                                                                                                                                                                |      |           |     |       |  |  |  |

|          | The server can read all incoming packets from the Internet.                                                                                                                                                                                                                                                                                                                                                                         | ✓    | <b>✓</b>  | (1) |       |  |  |  |

| 1(c)(i)  | Only one transmission is allowed on the bus at any one time // only one packet can be transmitted on the bus at any one time (1)  The two packets from A and B cannot both use the bus at the same time (1)  The attempts to transmit will be unsuccessful, because the stations will realise that the bus is busy (1)  Reference to CSMA/CD (1)  Collision causes a change in voltage of the bus (1)  1 mark for each point, max 2 |      |           |     |       |  |  |  |

| 1(c)(ii) | One mark for valid point, max 2  Calculate a random wait time Wait for the random time Check for idle bus // Check status of bus Attempt to re-transmit / re-send If unable to transmit, repeat process                                                                                                                                                                                                                             |      |           |     | 2     |  |  |  |

| Question | Answer                                                                                                                 | Marks |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|

| 1(d)(i)  | Star topology (1) Where each computer / device has its own <u>dedicated connection</u> to the server (1)               |       |  |  |  |  |  |  |

|          | Alternative answers:                                                                                                   |       |  |  |  |  |  |  |

|          | esh topology (1) very device connects directly to every other device (1)                                               |       |  |  |  |  |  |  |

|          | Ring topology (1) Use of tokens means no collisions // Every device examines every packet (1)                          |       |  |  |  |  |  |  |

| 1(d)(ii) | As each computer is now not sharing a single bus // has dedicated path (to the server) (1) Collisions cannot occur (1) |       |  |  |  |  |  |  |

|          | Alternative answers:                                                                                                   |       |  |  |  |  |  |  |

|          | Mesh As each device now has a direct path to all the others (1) Collisions cannot occur (1)                            |       |  |  |  |  |  |  |

|          | Ring Packets all travel in the same direction (1) Collisions cannot occur (1)                                          |       |  |  |  |  |  |  |

| Question | Answer                                                                                                                                                                                                                                                                                                                                                                                                                |           |              |      |        |       |      |      |      |    | Marks |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|--------|-------|------|------|------|----|-------|

| 2(a)     | Description                                                                                                                                                                                                                                                                                                                                                                                                           |           |              |      |        | Тур   | e of | proc | esso | or | 4     |

|          | It has a simplified set of instructions.                                                                                                                                                                                                                                                                                                                                                                              |           |              |      |        |       |      |      |      | _  |       |

|          | Emphasis is on the hardware rather than the software.                                                                                                                                                                                                                                                                                                                                                                 |           | <del>\</del> |      | _      |       |      | CISC |      |    |       |

|          | It makes extensive use of general purpose registers.                                                                                                                                                                                                                                                                                                                                                                  |           | _            |      |        |       | !    | RISC |      |    |       |

|          | Many instruction formats are available.                                                                                                                                                                                                                                                                                                                                                                               |           |              |      |        |       |      |      |      |    |       |

|          | 1 mark for each correct line                                                                                                                                                                                                                                                                                                                                                                                          |           |              |      |        |       |      |      |      |    |       |

| 2(b)(i)  | One mark per point – max 2  Pipelining is instruction level parallelism Execution (A: processing) of an instruction is split into a number of stages When first stage for an instruction is completed the first stage of the next instruction can start executing Another instruction can start executing before the previous one is finished Processing of a number of instructions can be concurrent / simultaneous |           |              |      |        |       |      |      | 2    |    |       |

| 2(b)(ii) |                                                                                                                                                                                                                                                                                                                                                                                                                       |           |              | Time | e Inte | erval |      |      |      |    | 3     |

|          | Stage                                                                                                                                                                                                                                                                                                                                                                                                                 | 1         | 2            | 3    | 4      | 5     | 6    | 7    | 8    |    |       |

|          | Fetch instruction                                                                                                                                                                                                                                                                                                                                                                                                     | D         | E            |      |        |       |      |      |      |    |       |

|          | Read registers and decode instruction                                                                                                                                                                                                                                                                                                                                                                                 |           | D            | Е    |        |       |      |      |      |    |       |

|          | Execute instruction                                                                                                                                                                                                                                                                                                                                                                                                   |           |              | D    | Е      |       |      |      |      |    |       |

|          | Access operand in memory                                                                                                                                                                                                                                                                                                                                                                                              |           |              |      | D      | Е     |      |      |      |    |       |

|          | Write result to register                                                                                                                                                                                                                                                                                                                                                                                              |           |              |      |        | D     | Е    |      |      |    |       |

|          | D at time interval 1 (1) D and E in second row (in that ord Remainder completed correctly                                                                                                                                                                                                                                                                                                                             | er)<br>(1 | (1<br>)      | )    |        |       |      |      |      |    |       |

© UCLES 2017 Page 4 of 12

## October/November 2017

| Question | Answer                                                                                                                                                                                                                          | Marks |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2(c)(i)  | Two from:                                                                                                                                                                                                                       | 2     |

|          | The result of the first addition is not stored in (register) r3 (1) Before the next instruction needs to load value from r3 (1) There is a data dependency issue (1) r3 is being fetched and stored on the same clock pulse (1) |       |

| 2(c)(ii) | The third instruction is not dependent on the first two, therefore, instruction 2 and 3 need to be swapped                                                                                                                      | 1     |

Page 5 of 12

| Question | Answer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Marks |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3(a)(i)  | A: Guest (operating system) (1) B: Host (operating system) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2     |

| 3(a)(ii) | One mark for each valid point, max 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3     |

|          | Guest OS (A) handles request as if it were running on its own physical machine // guest OS (A) is not aware it is running on a virtual platform Guest OS (A) handles the request as usual I/O requests are translated by the virtual machine software Into instructions executed by host OS (B) Host OS (B) retrieves the data from the file Host OS (B) passes the data to the virtual machine software The virtual machine software passes the data to the guest OS (A) Guest OS passes the data to the application |       |

| 3(b)(i)  | One mark from:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1     |

|          | Because software can be tried on different OS using same hardware Because no need to purchase / request all sorts of different hardware Easier to recover if software causes system crash VM provides protection to other software / host OS from malfunctioning software                                                                                                                                                                                                                                             |       |

| 3(b)(ii) | Max 2 marks per limitation, max 2 limitations – max 4 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4     |

|          | Virtual machine may not be able to emulate some hardware So that hardware cannot be tested using a virtual machine By relevant example, e.g. developing hardware drivers                                                                                                                                                                                                                                                                                                                                              |       |

|          | Using virtual machine means execution of extra code // processing time increased                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|          | so cannot accurately test speed of real performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|          | A virtual machine might not be as efficient By relevant example, e.g. might not be able to access sufficient memory                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Question | Answer                                                                                                                                                                                                                                                                                                                                                                               | Marks |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| 4(a)(i)  | Because a valid unsigned integer can be two digits / one or more digits (1)  Both 3 and 2 are digits (1)                                                                                                                                                                                                                                                                             |       |  |  |  |  |  |

| 4(a)(ii) | cause a valid unsigned number can be an unsigned integer followed by a cimal point followed by an unsigned integer (1)  is an unsigned integer and 5 is an unsigned integer (because it is a digit) d there is a point in between (1)  ernative response for 2 marks, combination of order and validity:  is a (valid) unsigned integer, followed by a decimal point, and 5 which is |       |  |  |  |  |  |

|          | another (valid) unsigned integer  Validity mark must refer to 32 and 5                                                                                                                                                                                                                                                                                                               |       |  |  |  |  |  |

| 4(b)     | <pre><unsigned number=""> ::=</unsigned></pre>                                                                                                                                                                                                                                                                                                                                       | 5     |  |  |  |  |  |

|          | <pre><unsigned_integer> ::=</unsigned_integer></pre>                                                                                                                                                                                                                                                                                                                                 |       |  |  |  |  |  |

|          | <pre></pre>                                                                                                                                                                                                                                                                                                                                                                          |       |  |  |  |  |  |

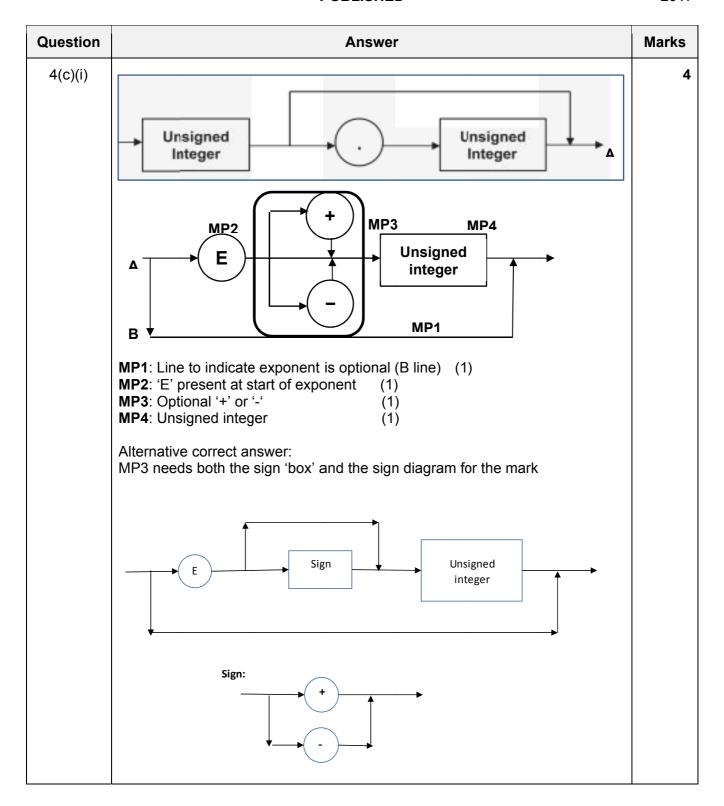

| Question | Answer                                         | Marks |

|----------|------------------------------------------------|-------|

| 4(c)(ii) | <pre><unsigned number=""> ::=</unsigned></pre> | 4     |

| Question |                                                                                                                                                                                                                                                                                                                                                            |            |                | Ans     | swer |     |     | Marks |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|---------|------|-----|-----|-------|

| 5(a)     | A                                                                                                                                                                                                                                                                                                                                                          | В          |                | X       |      |     |     | 1     |

|          | 0                                                                                                                                                                                                                                                                                                                                                          | 0          |                | 1       |      |     |     |       |

|          | 0                                                                                                                                                                                                                                                                                                                                                          | 1          |                | 0       |      |     |     |       |

|          | 1                                                                                                                                                                                                                                                                                                                                                          | 0          |                | 0       |      |     |     |       |

|          | 1                                                                                                                                                                                                                                                                                                                                                          | 1          |                | 0       |      |     |     |       |

|          |                                                                                                                                                                                                                                                                                                                                                            |            | •              |         | _    |     |     |       |

| 5(b)     |                                                                                                                                                                                                                                                                                                                                                            | Г          |                | T       | 1    | T — | 1   | 4     |

|          |                                                                                                                                                                                                                                                                                                                                                            |            | S              | R       | Q    | Q   |     |       |

|          | Initia                                                                                                                                                                                                                                                                                                                                                     | ally       | 1              | 0       | 1    | 0   |     |       |

|          | S change                                                                                                                                                                                                                                                                                                                                                   | ed to 0    | 0              | 0       | 1    | 0   | (1) |       |

|          | R chang                                                                                                                                                                                                                                                                                                                                                    | ed to 1    | 0              | 1       | 0    | 1   | (1) |       |

|          | R chang                                                                                                                                                                                                                                                                                                                                                    | ed to 0    | 0              | 0       | 0    | 1   | (1) |       |

|          | S and R cha                                                                                                                                                                                                                                                                                                                                                | anged to 1 | 1              | 1       | 0    | 0   | (1) |       |

| 5(c)(i)  | Clock (pulse)                                                                                                                                                                                                                                                                                                                                              |            |                |         |      |     |     | 1     |

| 5(c)(ii) | Max 2 marks                                                                                                                                                                                                                                                                                                                                                | per proble | m – <b>m</b> a | ax 4 ma | arks |     |     | 4     |

|          | Problem 1 One combination of S and R gives NOT valid / indeterminate output // Q and Q have the same value The JK flip-flop does not allow for Q and Q to have the same value for any combination of inputs // Q and Q have to be complementary  Problem 2 Inputs may not arrive at the same time The JK flip-flop has a clock pulse to synchronise inputs |            |                |         |      |     |     |       |

| Question | Answer                                                                                                                            | Marks |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| 6(a)     | One mark for suitable sensor, one mark for justification Max one sensor, max two marks                                            | 2     |  |  |  |  |  |

|          | humidity to ensure that the plants have the right level of moisture in the air                                                    |       |  |  |  |  |  |

|          | pressure / proximity to detect whether the windows are open or closed condone 'check'                                             |       |  |  |  |  |  |

|          | moisture to ensure the water levels in the soil are correct                                                                       |       |  |  |  |  |  |

|          | light to ensure the light levels in the greenhouse are correct for plant growth to ensure the windows are closed when night falls |       |  |  |  |  |  |

|          | Accept pH sensor for one mark only                                                                                                |       |  |  |  |  |  |

|          | Accept CO <sub>2</sub> sensor for one mark only, accept gas or O <sub>2</sub> for one mark only                                   |       |  |  |  |  |  |

|          | Justification needs to answer the question why? Not just describe the sensor                                                      |       |  |  |  |  |  |

|          | Accept suitable actions resulting from sensor readings as justification                                                           |       |  |  |  |  |  |

| 6(b)     | Three from:                                                                                                                       | 3     |  |  |  |  |  |

|          | Actions taken by system // or by example: e.g. adjust heater / turn on sprinkler / open windows                                   |       |  |  |  |  |  |

|          | May affect the readings taken by the sensors // or by example                                                                     |       |  |  |  |  |  |

|          | Which in turn may cause a change in the actions taken by the system // or by example                                              |       |  |  |  |  |  |

|          | This is a continuous process                                                                                                      |       |  |  |  |  |  |

| 6(c)(i)  | One from:                                                                                                                         | 1     |  |  |  |  |  |

|          | Lowest allowable temperature                                                                                                      |       |  |  |  |  |  |

|          | Highest allowable temperature                                                                                                     |       |  |  |  |  |  |

|          | Sampling time interval                                                                                                            |       |  |  |  |  |  |

| Question | Answer                                                                                                                                                                                                                                                                                                                                                 | Marks |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| 6(c)(ii) | If answer to c(i) is highest allowable or lowest allowable temperature:  The sensor reading is compared to a stored parameter (1) Depending upon result of comparison an action may or may not be carried out (1)  If answer to c(i) is sampling time interval:  The higher the sampling rate (1)The better / more efficient is the control system (1) |       |  |  |  |  |  |

| 6(d)(i)  | 20                                                                                                                                                                                                                                                                                                                                                     | 1     |  |  |  |  |  |

| 6(d)(ii) | LDD 4002  // load the contents of the 16 bit location containing the value for Sensor 5 into the Accumulator  LSR #8  // move the bits in the Accumulator so that the Accumulator stores the value of Sensor 5 as unsigned 16-bit binary integer  1 mark for 4002  1 mark for #8                                                                       | 3     |  |  |  |  |  |

https://xtremepape.rs/